# User Guide for ACQ2xx Embedded Web Pages

#### System Page: shows firmware versions and environment

| home | sysmon     | system    | signals | events  | phases | burst | vin    | dio  | cal  | AO | DIO32 |

|------|------------|-----------|---------|---------|--------|-------|--------|------|------|----|-------|

| acq  | acq-timing | acq-histo | ints    | tblocks | regs   | fpga  | tweaks | dmac | ppmu | mu | AZ    |

Capture Buffer Length: 402653184 0x18000000 384M

Linux version 2.6.11.11-acgX00 (pgm@islay) (gcc version 3.4.1) Linux Version:

#75 Sun Sep 18 18:42:27 BST 2005

version 211 date:200512082214 Initrd Version: version 1317 date:200512091442 Extra Version:

\$ld: acq200-fifo.c,v 1.14 2005/11/05 22:34:08 pgm Exp \$ Build 1156 Dec 6 2005 22:39:10\$ld: Driver Version:

acq196-fifo.c,v 1.6 2005/10/03 15:01:35 pgm Exp \$ \$ld: acq200-fifo-procfs.c,v 1.11 2005/12/09

14:40:59 pgm Exp \$ Build 1078 Dec 9 2005 14:41:07

serialnum=d30001

MODULES=/usr/local/lib/modules

AICHAN=96

acg100=acg196 Bootloader Environment: TERM=vt102

gEmac0=16:01

hostname=acq196 001

ip0=dhcp

eth0: 192.168.0.156

10411 acq196\_001 http://acq196\_001/cgi-bin/system.cgi Thu Dec 29 15:46:28 UTC 2005

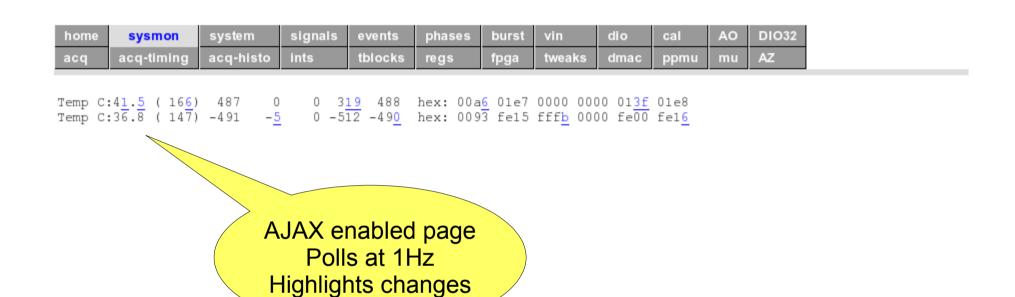

# sysmon Page: temperature monitoring.

# Signals Page: view and assign signals

|                   | mon<br>-timing                                | system<br>acq-histo | signals<br>ints | events<br>tblocks | phases<br>regs             | burst<br>fpga | vin<br>tweak |                          | io<br>mac       | cal<br>ppmu         | AO<br>mu                 | DIO32<br>AZ |

|-------------------|-----------------------------------------------|---------------------|-----------------|-------------------|----------------------------|---------------|--------------|--------------------------|-----------------|---------------------|--------------------------|-------------|

| Signal<br>ext_clk | Setting<br>DI0                                | falling inactive    | )               | ris               | Signal<br>ext_clk<br>ing   | d0            | d1           | d2                       | ine<br>d3       | d4                  | d5                       | none        |

| int_clk_src       | DIO                                           | falling inactive    | •               |                   | ling<br>int_clk<br>ing     | 0<br>d0       | C<br>d1      | C d2                     | d3              | d4                  | d5                       | none        |

| ao_clk            | DI0                                           | falling inactive    | Solo            | ct Val            |                            | d0            | Cl<br>d1     | d2                       | C<br>d3         | d4                  | C<br>d5                  | none        |

| ao_trig           | DI3                                           | fal                 | Use "I<br>view  | ogrea<br>what     | d" to                      |               | 0<br>d1      | 0<br>0<br><b>d2</b><br>0 | C<br>d3<br>C    | 0<br>0<br><b>d4</b> | 0<br>0<br><b>d5</b><br>0 | none        |

| sync_trig_src     | DI3                                           | falling inactive    | inpt oo         |                   | mg_sro                     | d0            | d1           | d2                       | d3              | d4                  | d5                       | none        |

| counter_src       | DI6                                           | falling ACTIVE      | Ē               | fal               | ing<br>ling<br>counter_src | 0<br>0        | 0<br>0<br>d1 | 0<br>0<br>d2             | ()<br>()<br>(d3 | C<br>C<br>d4        | 0<br>0<br>d5             | internal    |

| sync_trig_ma      | s DO3                                         | inactive            | )               | sv                | nc_trig_ma                 | s d0          | C<br>d1      | C d2                     | C<br>d3         | C d4                | ①<br>d5                  | none        |

| mas_clk           | none                                          |                     |                 | -,                | mas_clk                    | d0            | C<br>d1      | 0<br>d2<br>0             | d3              | C<br>d4             | 0<br>d5                  | none        |

| 10425 ac          | 10425 acq196_001 Thu Dec 29 15:46:42 UTC 2005 |                     |                 |                   |                            | http://a      | acq196_      | _001/c                   | gi-bin/s        | signals.c           | gi                       |             |

# Events Page: view and assign Events

| home | sysmon     | system    | signals | events  | phases | burst | vin    | dio  | cal  | AO | DIO32 |

|------|------------|-----------|---------|---------|--------|-------|--------|------|------|----|-------|

| acq  | acq-timing | acq-histo | ints    | tblocks | regs   | fpga  | tweaks | dmac | ppmu | mu | AZ    |

| Func   | Actual                      | Function       |     |      | Li | ne |    |     |         |

|--------|-----------------------------|----------------|-----|------|----|----|----|-----|---------|

| trig   | trig DI3 falling inactive   | trig           | d   | 0 d1 | d2 | d3 | d4 | 1 0 | 15 none |

|        |                             | rising         | 0   | 0    | 0  | 0  | 0  | 0   | 0       |

| 10     | - IO DIO CALLANDIA          | falling        | 0   | 0    | 0  | 0  | 0  | 0   |         |

| event0 | event0 DI3 falling inactive | event0         | d   | 0 d1 | d2 | d3 | d4 | 1 0 | 15 none |

|        |                             | rising         | 0   | 0    | 0  | 0  | 0  | 0   | 0       |

| event1 | event1 DI3 rising inactive  | falling        | 0   | 0    | 0  | 0  | 0  | 0   |         |

|        | overm the manny macare      | event1         | d   | 0 d1 | d2 | d3 | d4 | 1 0 | 15 none |

|        |                             | rising         | 0   | 0    | 0  | 0  | 0  | 0   | 0       |

|        |                             | falling        | 0   | 0    | 0  | 0  | 0  | 0   |         |

|        |                             | counter_update | smp | e0   | e1 |    |    |     |         |

|        |                             |                | (*) | 0    | 0  |    |    |     |         |

Trigger: Optional Signal starts the capture process

Event0: Optional signal causes phase transition from PRE- to POST-

Event1: Second, special purpose Event

|  | 10435 | acq196_001 | Thu Dec 29 15:46:52 UTC 2005 | http://acq196_001/cgi-bin/events.cgi |

|--|-------|------------|------------------------------|--------------------------------------|

|--|-------|------------|------------------------------|--------------------------------------|

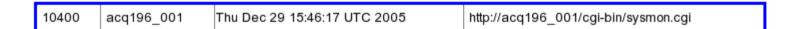

## Burst Page: controls multiframe streaming mode

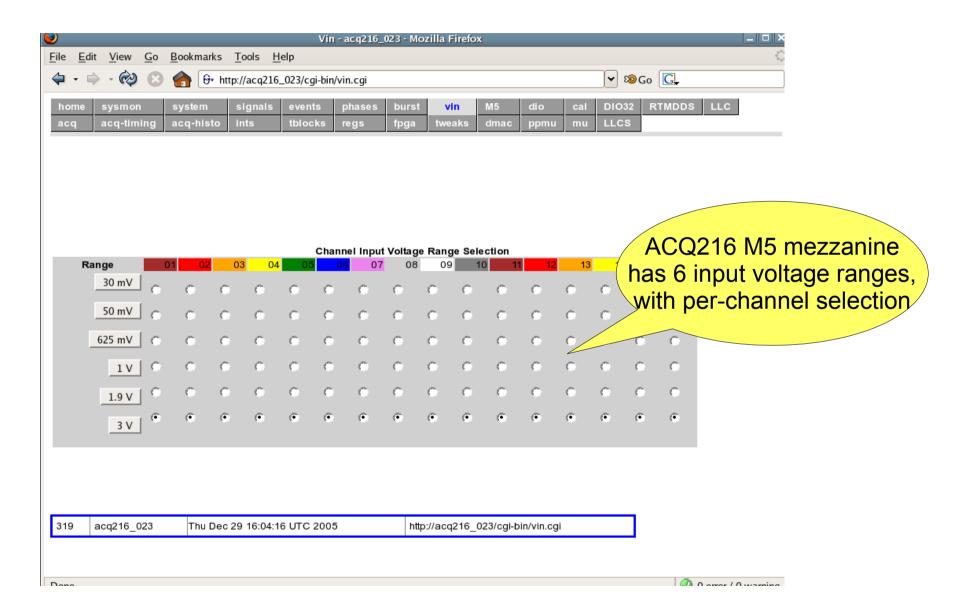

#### Vin Page: view/control input voltage range selection

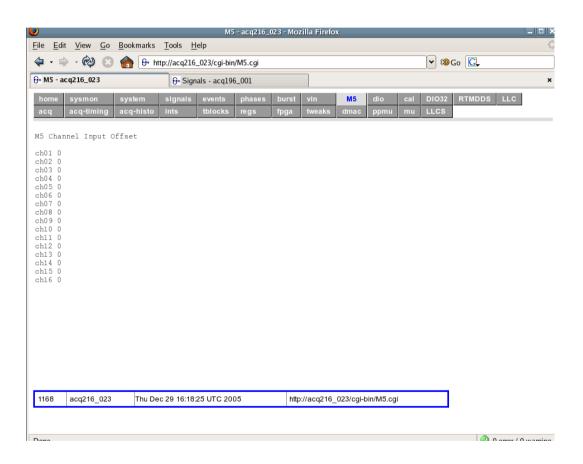

# Personality Specific Page – displays M5 input offset

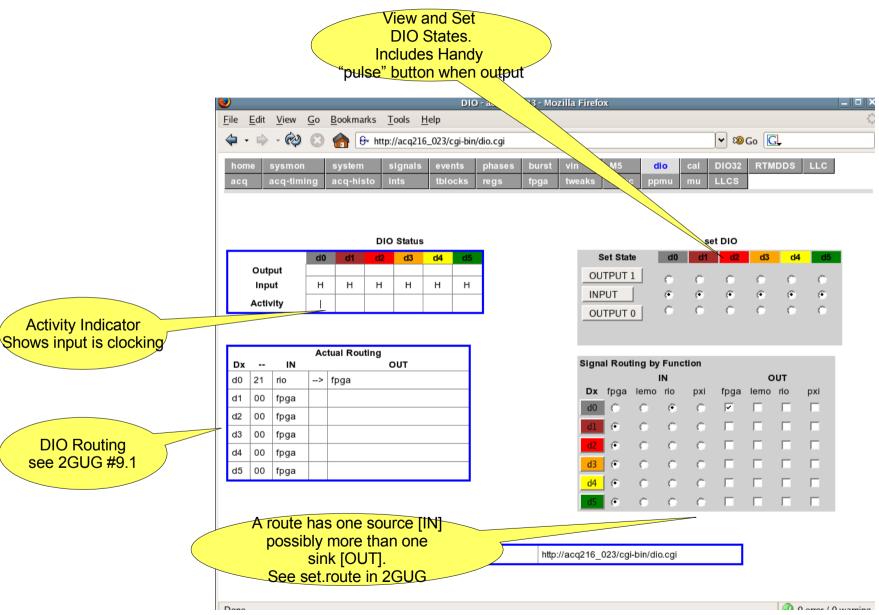

## DIO Specific Page – monitor, set DIO, set DIO routings

#### Calibration and board specific details held in XML file:

```

Mozilla Firefox

Edit View Go Bookmarks Tools Help

♥ ‱Go C↓

http://acq216_023/etc/cal/caldef.xml

This XML file does not appear to have any style information associated with it. The document tree is shown below.

- <ACO>

m5-default.xml $Revision: 1.7 $

this is the default m5 range config file

add calibration data if available via <Calibrated> fields

<!-- calibration data -->

- <AcqCalibration>

- <Info>

<CalDate>20051221:18:02</CalDate>

<Version>$RCSfile: calibrate.cpp,v $ $Revision: 1.9 $ B1016</Version>

<Model>ACQ216-M5</Model>

<Serialnum>d41023</Serialnum>

</Info>

on M5 switch assignment is adjacent AB values in register

so logical range key by {ADC_RANGE, GAINA, GAINB} does not refer directly

to a physical device for the latter two fields.

mapping handled by M5 custom class in vin program,

using SWPHYS attribute. Range selection is:

ADC_RANGE 0=1V, 1=1.6V

GAINA, GAINB 0,0:G1, 1,0:G2, 1,1:G4

- <Data AICHAN="16" polarity="REVERSED" SW="ADC_RANGE,M5_GAINA,M5_GAINB"

SWPHYS="ADC_RANGE,M5/GAIN.01-08,M5/GAIN.09-16">

- <Range name="30" sw="0,1,1">

<Nominal min="-0.031" max="0.031"/>

</Range>

```

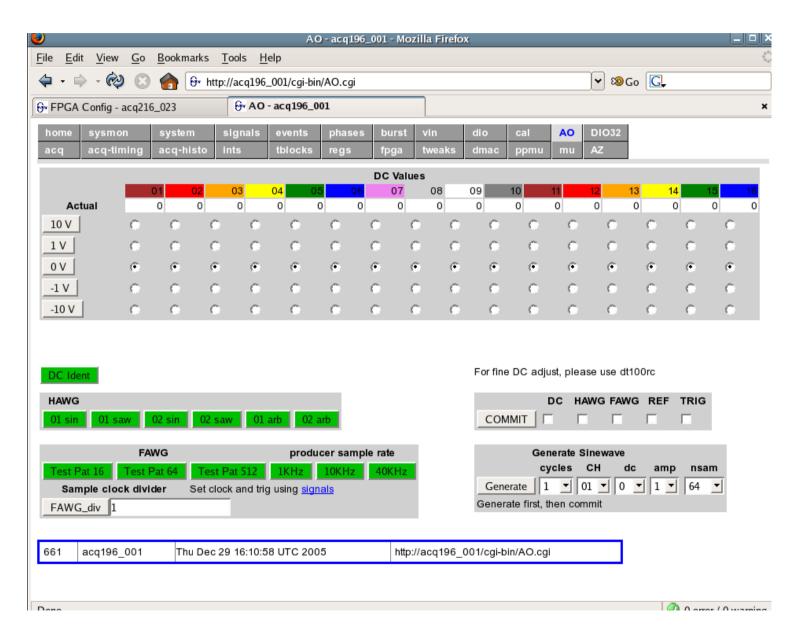

#### AO Page – ACQ196-RTMAO – DC settings, simple AWG functionality

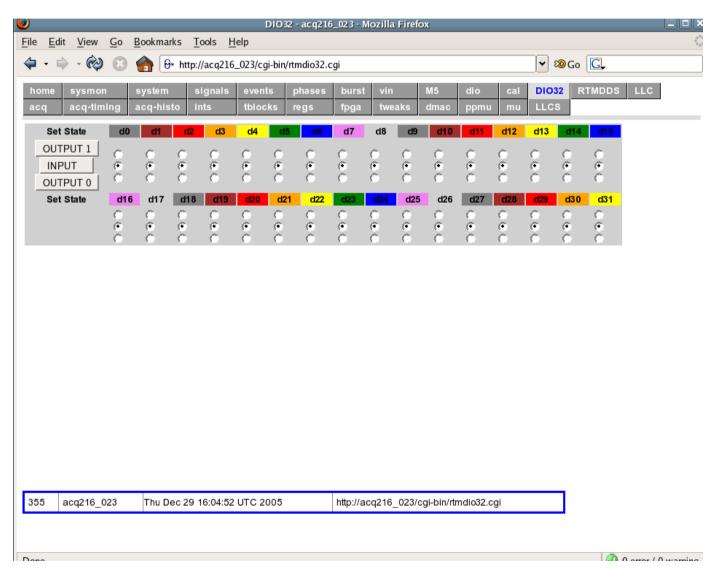

# DIO32 – set direction and value for 32bit DIO registers

#### Capture Stats – information about last shot

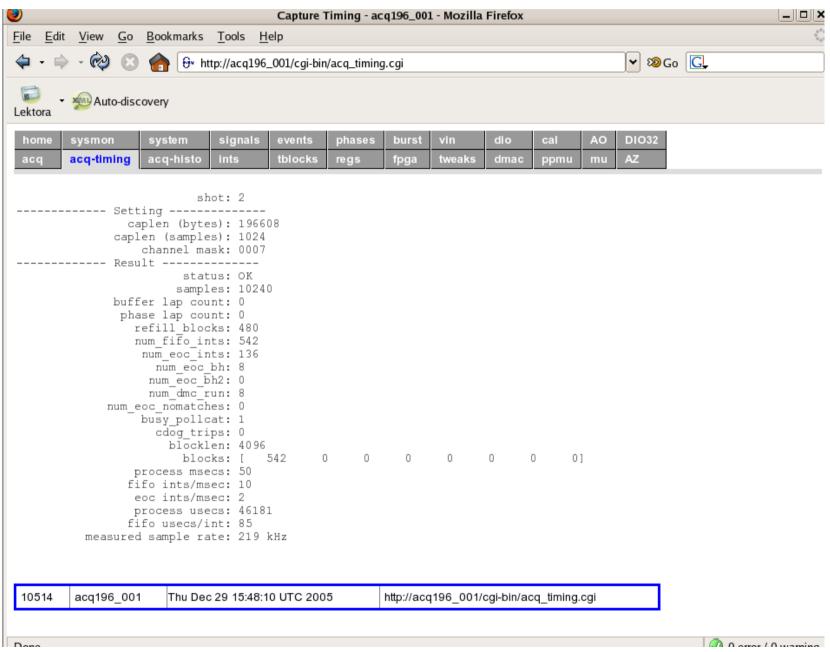

## Capture Timing – information about last shot

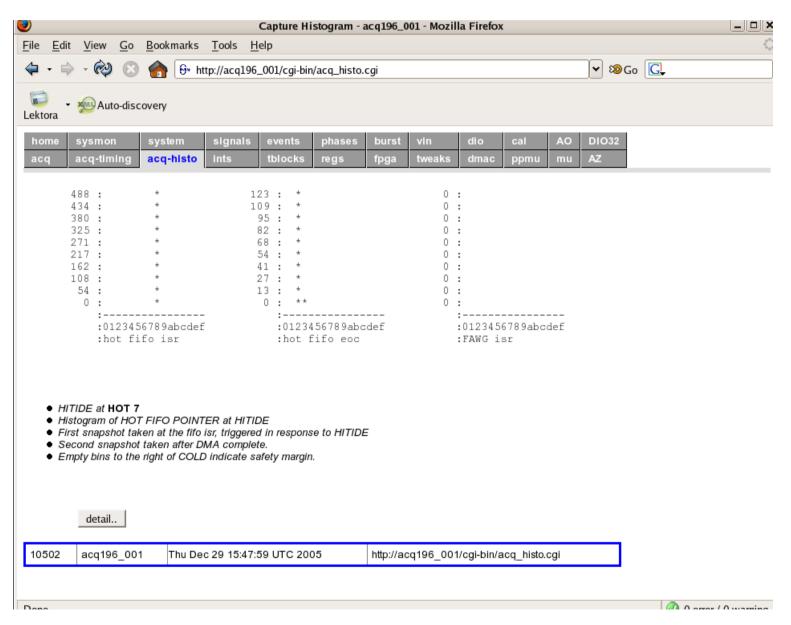

## Capture Histogram – a measure of system real time performance

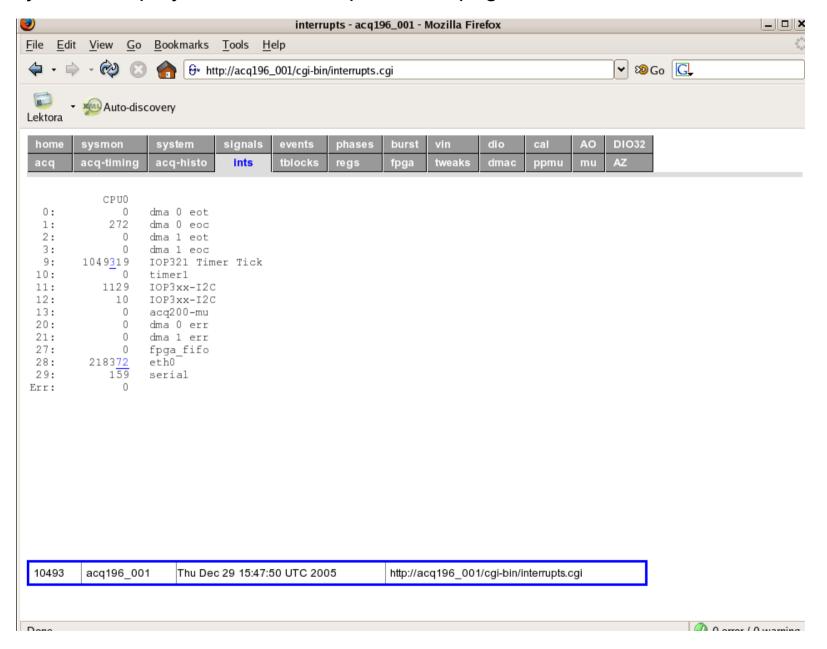

# Ints: dynamic display of Linux interrupts status page

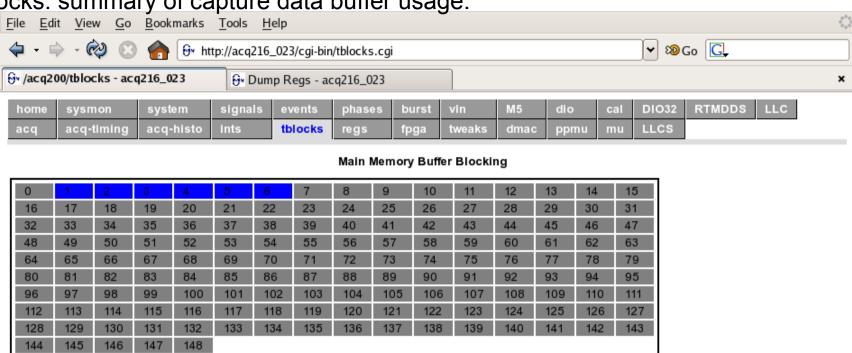

Tblocks: summary of capture data buffer usage.

Buffer memory is divided into 6MB "Tblocks" and acquisition proceeds cyclically round the buffer. During capture, the "RAW" blocks show the current data set with data in raw format. Post shot, data is transformed into "COOKED" format for fast data access. Data may also be reserved during the shot as part of a "PREP", this is indicated as a "SHARED" block"

| 588 | acq216_023 | Thu Dec 29 16:08:45 UTC 2005 | http://acq216_023/cgi-bin/tblocks.cgi |

|-----|------------|------------------------------|---------------------------------------|

|     |            |                              |                                       |

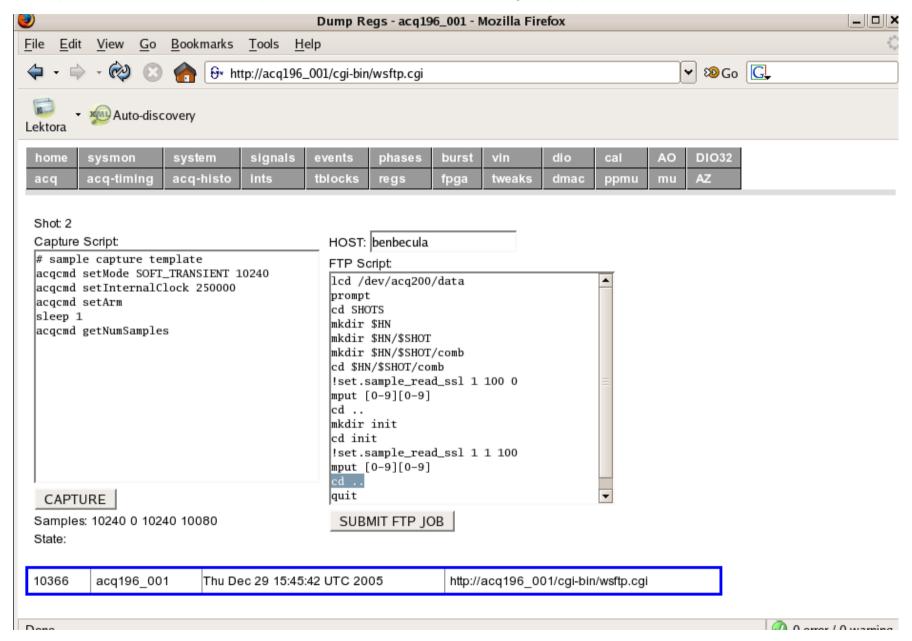

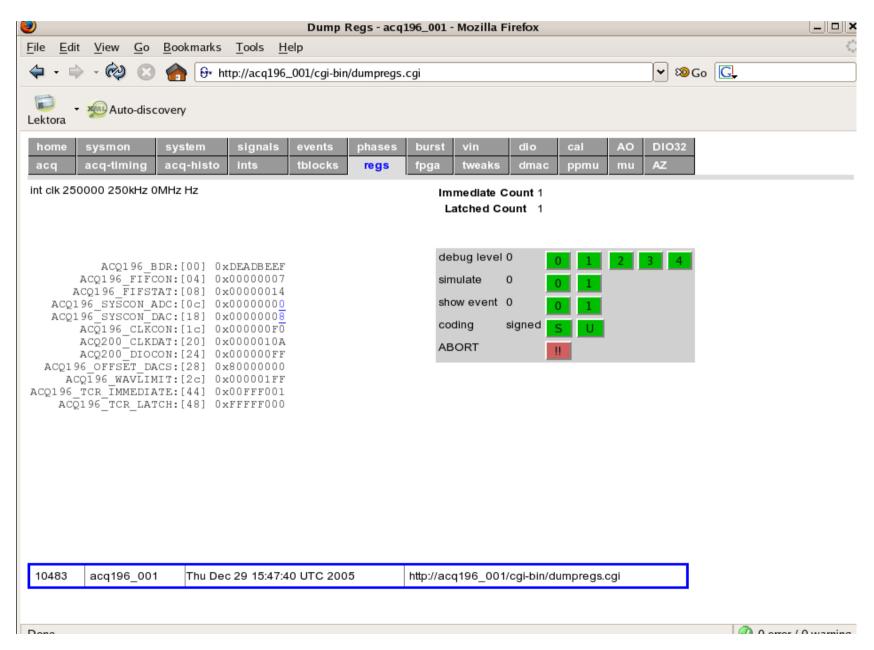

#### Dumpregs: diagnostic dump of FPGA registers

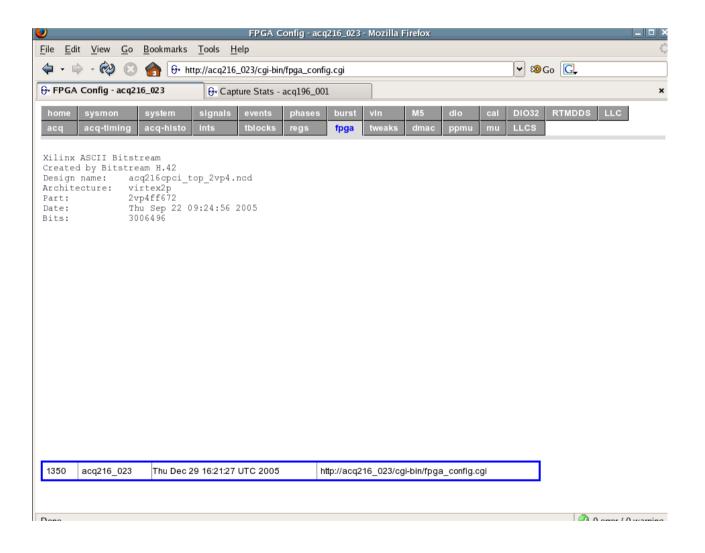

# FPGA Config – information about fpga image

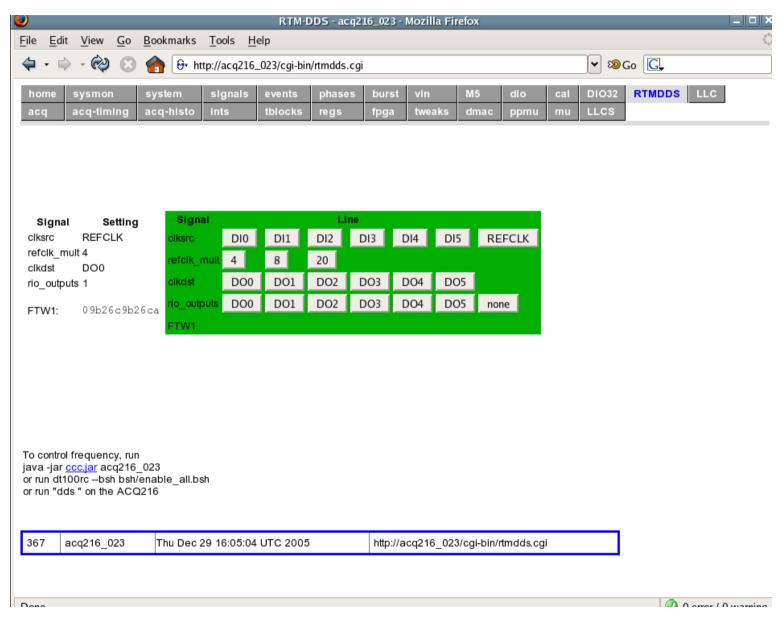

# RTM\_DDS – Custom RTM frequency and routing control

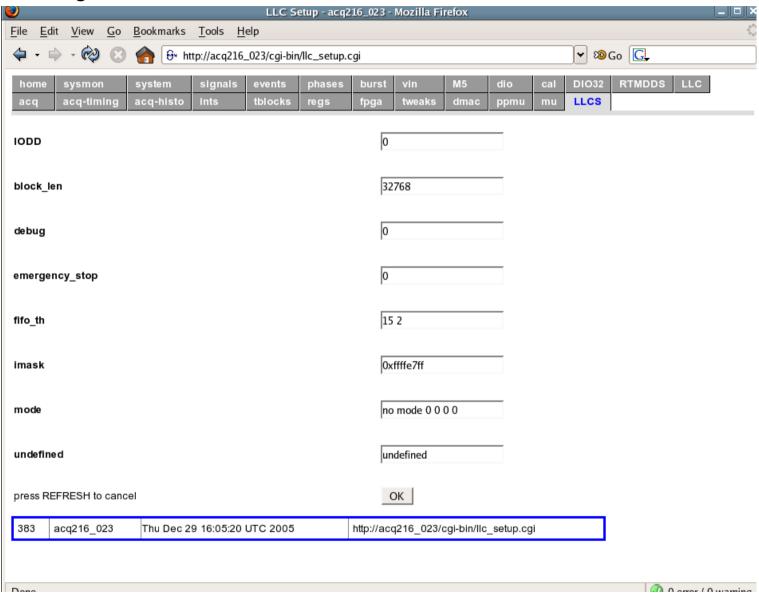

# LLC Settings – controls for custom kernel module

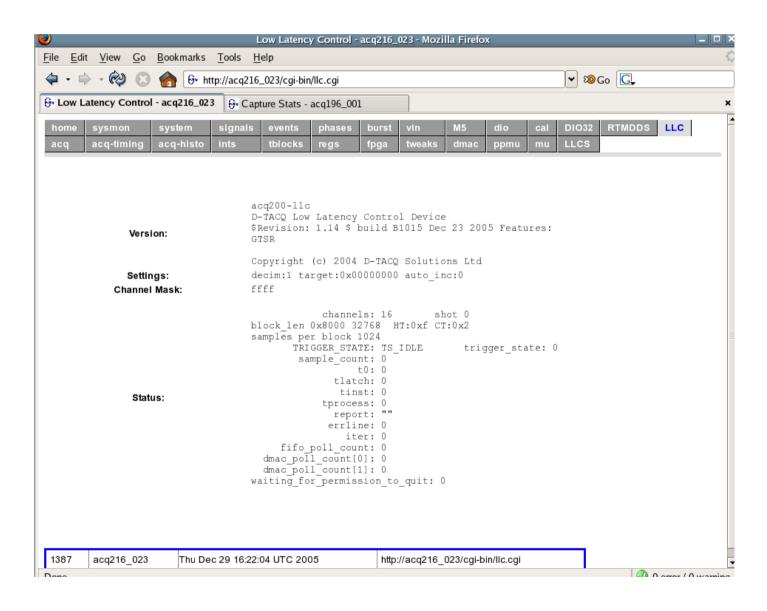

### LLC Status – status report for custom control module

## Example CGI form for capture control, followed by ftp upload.